Serial In /Serial Out

[KEMBALI KE MENU SEBELUMNYA]

DAFTAR ISI

1. Tujuan [kembali]

Memahami cara kerja pergeseran data secara serial dalam register shift.

-

Mengidentifikasi aplikasi register SISO dalam sistem komunikasi dan penyimpanan data.

-

Mempelajari implementasi rangkaian SISO menggunakan flip-flop dan logika digital.

2. Alat dan Bahan[kembali]

Jenis kedua adalah gerbang OR. Sama seperti gerbang sebelumnya, gerbang ini juga memerlukan dua input untuk menghasilkan satu output. Gerbang OR ini akan menghasilkan output 1 jika semua atau salah satu input merupakan bilangan biner 1. Sedangkan output akan menghasilkan 0 jika semua inputnya adalah bilangan biner 0.

3. Dasar Teori[kembali]

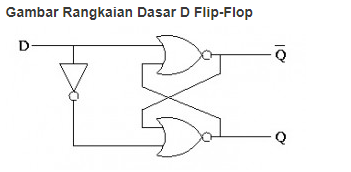

Gambar Rangkaian Dasar D Flip-Flop Pada gambar diatas input Set (S) dihubungkan ke input Reset (R) pada RS flip-flop menggunakan sebuah inverter sehingga terbentuk input atau masukan baru yang diberi nama input Data (D). Dengan kondisi tersebut maka RS flip-flop berubah menjadi Data Flip-Flop (D-FF). Pada perkembanganya D flip flop ini ditambahkan dengan input atau masukan control berupa enable/clock seperti ditunjukan pada gambar berikut.

2. Logic State

status logika Pengertian logis, benar atau salah, dari sinyal biner yang diberikan. Sinyal biner adalah sinyal digital yang hanya memiliki dua nilai yang valid. Dalam istilah fisik, pengertian logis dari sinyal biner ditentukan oleh level tegangan atau nilai arus sinyal, dan ini pada gilirannya ditentukan oleh teknologi perangkat. Dalam sirkuit TTL, misalnya, keadaan sebenarnya diwakili oleh logika 1, kira-kira sama dengan +5 volt pada garis sinyal; logika 0 kira-kira 0 volt. Tingkat tegangan antara 0 dan +5 volt dianggap tidak ditentukan

3. Serial-In Serial-Out

Rangkaian register geser SISO menerima data serial pada pin input-nya dan menggesernya keluar secara serial pada pin output-nya. Jumlah bit yang dapat digeser keluar sebelum bit berikutnya tiba bergantung pada kecepatan sinyal clock yang mengendalikan operasi register geser. Jenis register geser ini dapat digunakan sebagai penyangga antara dua perangkat asinkron yang berkomunikasi satu sama lain menggunakan sinyal dengan frekuensi atau fase yang berbeda.

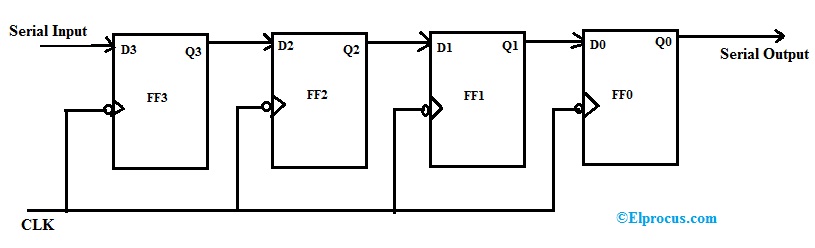

Diagram blok register geser SISO ditunjukkan di bawah ini, yang mencakup flip-flop 3-D. Koneksi FF ini dapat dilakukan dengan menghubungkan keluaran Flip-Flop yang satu ke masukan flip-flop berikutnya. Jadi, FF ini sinkron satu sama lain karena sinyal CLK yang sama diterapkan pada setiap Flip-Flop.

Register geser ini hanya memiliki tiga koneksi: SI (masukan serial), SO (keluaran serial), dan CLK (sinyal clock). Di sini, SI menentukan masukan yang masuk ke flip-flop sisi kiri, SO adalah keluaran yang diambil dari flip-flop sisi kanan & sinyal CLK sekuensing.

Pada register geser jenis ini, bit-bit dapat ditransmisikan secara serial dari masukan serial flip-flop. Untuk setiap sinyal clock dalam FF, data dapat ditransmisikan dari satu fase ke fase berikutnya. Hasilnya, kita bisa mendapatkan bit-bit secara berurutan dari keluaran D-FF yang dikenal sebagai keluaran serial.

Diagram Sirkuit Register Pergeseran SISO

Diagram rangkaian register geser SISO ditunjukkan di bawah ini, di mana D-FF seperti D0 hingga D3 dihubungkan secara serial seperti yang ditunjukkan pada diagram berikut.

Mula-mula, keempat flip-flop D diatur ke modus reset sehingga keluaran masing-masing flip-flop dalam rangkaian adalah rendah, yaitu '0'.

Ini adalah rangkaian mode geser kanan, yang berarti ketika input/output data diberikan di ujung kiri flip-flop, bit yang tersimpan dapat digeser ke sisi kanan untuk menghasilkan keluaran serial. Sekarang mari kita bahas bagaimana data yang diberikan disimpan dalam register ini.

Cara Kerja Register Geser SISO

Mari kita ambil contoh bilangan biner 1011. Sebelum itu, rangkaian harus diatur ke mode reset agar keluaran setiap register menjadi '0', sehingga keluaran yang dihasilkan oleh semua register adalah "0000".

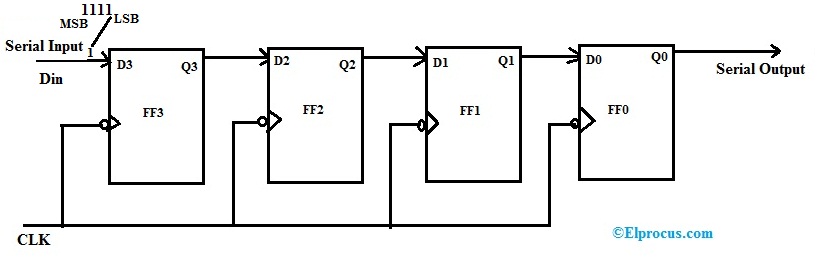

Dalam contoh register geser 4-bit seperti "1111", bit LSB adalah '1' dan bit MSB adalah '1'. Pertama, sinyal tinggi (bit LSB) digunakan sebagai input ke flip-flop D3 pertama, kemudian D3 = 1. Namun, pada prinsipnya, semua output D FF akan bernilai 0. Jadi, D2 = D1 = D0 = 0. Ketika input D3 bersinyal tinggi (1), maka D3 akan menyebabkan 'Q3' bernilai '1'. Oleh karena itu, output daya keseluruhan untuk tepi jatuh pertama akan menjadi 1000.

Demikian pula, ketika bit input data berikutnya dalam sinyal tinggi 4-bit (1) diberikan pada flip-flop D3, 'D3' ini akan menyebabkan 'Q3' menjadi 1, namun, 'Q3' diberikan sebagai input ke FF 'D2'. Jadi, 'D2' ini akan menyebabkan 'Q2' menjadi 1 ketika semua output yang tersisa akan menjadi 0.

Hasilnya, kita akan memperoleh '11' untuk tepi jatuh ke-2; jadi akan memperoleh '11' pada bit yang disimpan dalam register geser, sehingga o/p keseluruhan untuk tepi jatuh ke-2 akan memperoleh o/p sebagai “1100”.

Selain itu, bit MSB seperti sinyal tinggi (1) diberikan sebagai input, setelah itu '1' pada 'Q1' akan menyebabkan input 'D0' menjadi '1', sehingga 'Q0' menjadi '1'. Oleh karena itu, akhirnya, SISO menyimpan bit 1111 & ditampilkan di output daya.

4. IC 74HC166

Rangkaian Logika Internal IC 74HC166

Diagram paling kiri menunjukkan bagaimana logika internal dari 74HC166 bekerja:

Komponen Kunci:

-

8 buah Flip-Flop D (register D): menyimpan bit A–H.

-

Gerbang AND dan OR: menentukan apakah register akan menerima data dari input paralel atau dari data serial (shift).

-

SER (Serial Input): digunakan saat data dimasukkan satu per satu.

-

SH/LD (Shift/Load): kontrol utama untuk memilih antara mode paralel (load) dan mode shift.

-

CLK dan CLK INH: sinyal clock dan inhibisi clock.

-

CLR (Clear): untuk mereset semua register menjadi 0.

Jalur Aliran Data:

-

Saat

SH/LD = 0, data dari input paralel (A–H) dimasukkan langsung ke flip-flop melalui jalur atas. -

Saat

SH/LD = 1, jalur input paralel diputus, dan flip-flop menerima data dari jalur shift serial. -

Tiap flip-flop menerima data dari flip-flop sebelumnya saat puls clock aktif (edge naik).

-

Bit terakhir akan keluar di pin Qh.

(b) Simbol Logika IC 74HC166

Simbol ini mewakili bentuk IC dalam diagram rangkaian:

| Pin | Fungsi |

|---|---|

| A–H | Input paralel (8 bit) |

| SER | Input data serial |

| SH/LD | Pilih mode shift atau load |

| CLK | Clock (sinyal penggeseran) |

| CLK INH | Clock inhibit (aktif tinggi, menonaktifkan clock) |

| CLR | Clear (reset register ke 0) |

| Qh | Output serial |

3a. Contoh soal [kembali]

Soal 1: Operasi Pergeseran Serial

Sebuah IC 74HC166 digunakan dalam mode shift (SH/LD = 1), dengan kondisi awal semua output bernilai 0. Input SER diberikan data 1, kemudian diberikan 4 pulsa clock berturut-turut sambil mempertahankan SER = 1. Berapakah nilai output Qh setelah 4 pulsa clock?

Jawaban:

Qh = 1

Penjelasan:

Setiap pulsa clock akan menggeser bit ke kanan, dan memasukkan 1 dari SER. Setelah 4 clock, register berisi 1111, dan bit paling kanan (Qh) adalah 1.

Soal 2: Operasi Load Paralel

Sebuah sistem digital menggunakan IC 74HC166 untuk menyimpan data 8-bit secara paralel. Nilai input paralel A sampai H adalah 10101010, dan sinyal SH/LD diberikan 0 (low) sementara CLR = 1. Ketika diberikan satu pulsa clock, data paralel dimuat ke register. Apa nilai Qh sesaat setelah data dimuat?

Jawaban:

Qh = 0

Penjelasan:

Saat SH/LD = 0, data paralel langsung masuk. Bit H (MSB) adalah 1, dan A (LSB) adalah 0. Namun, Qh adalah output dari bit terakhir, yaitu A. Jadi Qh = 0.

Soal 3: Operasi Reset

Sebuah rangkaian menggunakan IC 74HC166 yang telah menyimpan data 11001100 secara paralel sebelumnya. Karena terjadi kesalahan, sistem ingin menghapus semua isi register. Sinyal CLR diberikan logika 0 sejenak. Apa kondisi semua bit dan Qh setelah itu?

Jawaban:

Semua bit = 0, Qh = 0

Penjelasan:

Ketika CLR = 0, IC akan mereset semua isi register tanpa memerlukan clock. Artinya, seluruh isi register akan bernilai 0, dan output Qh juga menjadi 0.

3b. Example[kembali ]

Example 1: Input Ekspansi untuk Mikrokontroler

Sebuah sistem mikrokontroler ingin membaca 8 buah tombol (push button), tetapi hanya tersedia 3 pin input digital. Untuk mengatasi keterbatasan pin, digunakan IC 74HC166 sebagai serial input register.

Rangkaian:

-

Ke-8 tombol dihubungkan ke input paralel A–H pada 74HC166.

-

SH/LD di-set LOW sejenak untuk meload data tombol secara paralel.

-

Setelah itu SH/LD di-set HIGH, dan dengan setiap pulsa clock, data tombol dikirim satu per satu melalui pin Qh ke mikrokontroler.

-

Mikrokontroler hanya menggunakan 3 pin:

-

Satu untuk SH/LD

-

Satu untuk Clock

-

Satu untuk Membaca Qh

-

Hasil:

Mikrokontroler bisa membaca semua status tombol (ON/OFF) secara efisien hanya dengan 3 pin input, menghemat I/O pin dan sangat berguna untuk proyek dengan banyak input seperti panel kontrol.

Example 2: Buffer Serial Input pada Sistem Komunikasi Digital

Deskripsi:

Dalam suatu rangkaian komunikasi digital sederhana, data dari sensor dikirim secara serial ke sistem pemrosesan utama. Untuk memastikan tidak ada kehilangan data saat pemrosesan lambat, digunakan 74HC166 sebagai shift register buffer.

Rangkaian:

-

Input serial dari sensor dikirim ke pin SER IC 74HC166.

-

Setiap kali data masuk, pulsa clock diberikan dan data digeser ke dalam register.

-

Setelah 8 bit terkumpul, SH/LD di-set LOW dan mikrokontroler membaca seluruh isi register secara paralel untuk diproses.

Hasil:

Data dari sensor dapat diterima terus-menerus secara serial, disimpan sementara di dalam register, dan kemudian diproses sekaligus, mengurangi beban CPU dan risiko kehilangan bit akibat delay.

3c. Pilihan ganda[kembali ]

1. Ketika pin SH/LD pada IC 74HC166 diberi logika LOW (0) dan CLR = HIGH (1), maka:

A. Register akan melakukan pergeseran data dari SER

B. Data dari pin A–H akan dimuat ke register

C. Register akan dikosongkan

D. Output Qh menjadi tidak terdefinisi

Jawaban: B

Penjelasan:

SH/LD = 0 berarti load paralel aktif → data dari input A–H langsung dimasukkan ke flip-flop.

2. Apa fungsi dari pin CLR (clear) pada IC 74HC166?

A. Mengaktifkan clock

B. Memuat data paralel

C. Menyalakan semua output

D. Mereset seluruh isi register menjadi 0

Jawaban: D

Penjelasan:

Pin CLR aktif LOW → bila CLR = 0, maka seluruh isi register diset ke 0, termasuk output

3Jika SER = 1 dan diberikan 3 pulsa clock dalam mode shift (SH/LD = 1), maka:

A. Tiga bit pertama dalam register akan bernilai 1

B. Semua output akan 0

C. Output Qh tidak berubah

D. Hanya bit A yang bernilai 1

Jawaban: A

Penjelasan:

Setiap pulsa clock akan memasukkan 1 ke register dari pin SER. Maka setelah 3 clock, tiga bit pertama (A, B, C) berisi 1.

4. Percobaan[kembali ]

Langkah-Langkah Percobaan:

1. Rangkai Komponen Seperti Gambar

-

Gunakan IC 74HC166.

-

Hubungkan input paralel D0–D7 ke 8 saklar (switch).

-

Hubungkan pin SI (Serial Input) ke LOW (0).

-

Hubungkan pin kontrol:

-

SH/LD ke saklar (untuk dikendalikan HIGH/LOW)

-

MR (Master Reset) ke HIGH (selalu aktif)

-

CLK ke tombol push button

-

CLK INH ke LOW (aktifkan clock)

-

-

Hubungkan SO (pin 13) ke LED atau probe logika.

2. Set Data pada Input Paralel

Misalnya:

-

D7 = 1

-

D6 = 0

-

D5 = 1

-

D4 = 0

-

D3 = 1

-

D2 = 0

-

D1 = 1

-

D0 = 0

Jadi data =10101010

3. Aktifkan Mode Load

-

Set SH/LD = 0

-

Tekan tombol clock sekali (atau bisa juga tanpa clock, karena data dimuat langsung saat SH/LD = 0)

-

Data

10101010dimuat ke dalam register dari D7 (MSB) hingga D0 (LSB)

4. Aktifkan Mode Shift

-

Set SH/LD = 1

-

Tekan tombol Clock beberapa kali

-

Setiap clock akan menggeser data satu bit ke kanan, dan keluaran muncul di SO/Qh

5. Amati Output

-

Setelah setiap clock ditekan:

-

Bit D7 keluar pertama di SO

-

Lalu D6, D5, ..., D0

-

-

Misalnya: Clock 1 → SO = 1 (D7), Clock 2 → SO = 0 (D6), dst.

5. Video[kembali ]

6. Download File[kembali ]

- Download File Rangkaian klik disini

- Download Video Rangkaian klik disini

.jpg)

Komentar

Posting Komentar